(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

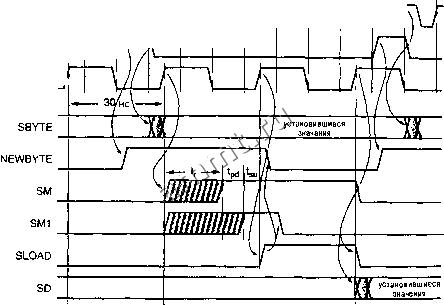

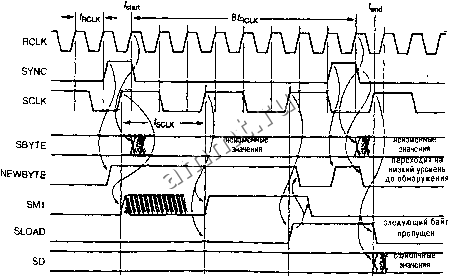

Читальный зал --> Программные средства foundation RCLK SYNC SCLK -110 не I- I-- 80нс-►  Рис. 8.107. Временные диаграммы для схемы SCTRL, приведенной на рис. 8.106 По поводу схемы на рис. 8.106 нужно сделать несколько замечаний. Во-первых, у сигнала SYNC не должно быть паразитных импульсов, хк. он подан на вход S защелки, и он должен быть достаточной длительности, чтобы удовлетворить требованию защелки к минимальной ширине импульса. Поскольку защелка устанавливается в единичное состояние по нарастающему фронту сигнала SYNC, получается, что мы немного смошенничали: сигнал NEWBYTE может возникнуть чуть раньше того момента, когда новый байт действительно будет доступен на выходах регистра HREG. Но это не страшно: прежде чем произойдет зафузка регистра SREG, пройдет два периода сигнала SCLK после того, как триггер FF1 увидит сигнал NEWBYTE. На самом деле, можно было словчить еще больше, если имеется опережающая версия сигнала SYNC (см. задачу 8.95). На рис. 8.107 приведены временные диаграммы для узла SCTRL с типичными временными соотношениями между сигналами. Поскольку сигналы SCLK и RCLK асинхронны, сигнал SCLK может произвольно располагаться на оси времени по отношению к сигналам RCLK и SYNC. На рисунке показан случай, когда очередной нарастающий фронт сигнала SCLK приходит спустя заметное время после возникновения сигнала NEWBYTE. Хотя на рисунке изображены окна, в которых сигналы SM и SM1 могли бы быть метастабильными в общем случае, однако в той ситуации, какая указана на рисунке, метастабильность, в действительности, не наступает. Позднее мы рассмотрим, что может произойти, если фронт сигнала SCLK совпадает по времени с изменением сигнала NEWBYTE.  Рис. 8.108. Временные диаграммы для схемы SCTRL в случае максимальной задержки Пусть время установления D-триггера равно t, а задержка распространения для вентиля И -1; тогда для выхода из метастабильности мы располагаем временем t, равным периоду сигнала SCLK (30 не) минус (t +1, как показано на рис. 8.107. Из временньгх диафамм также видно, почему нельзя воспользоваться непосредственно сигналом SM для сброса SR-защелки. Возможная метастабильность сигнала SM могла бы полностью нарушить работу схемы. Например, половинное по отношению к высокому уровню значение сигнала SM может оказаться достаточным, чтобы сбросить защелку, но затем сам сигнал SM может перейти обратно на низкий уровень, и тогда сигнал SLOAD не будет выработан и мы пропустим байт. Используя выходной сигнал синхронизирующего устройства (SLOAD) как для сброса защелки, так и в качестве сигнала зафузки в части интерфейса, управляемой тактовым сигналом SCLK, мы гарантируем, что новый байт будет обнаружен и надлежащим образом воспринят в обеих частях интерфейса, работающих с тактовыми сигналами RCLK и SCLK. Приведенные на рис.8.107 временнь/е диафаммы относятся к штатной ситуации, но нам необходимо проанализировать также, что произойдет при другом сдвиге по времени между сигналом SCLK и сигналами RCLK и SYNC, нежели тот, какой указан на рисунке. Вы, наверное, сами сможете убедиться в том, что все будет работать хорошо, как и в рассмотренном случае, если фронт сигнала SCLK придется на тот интервал времени, когда сигнал NEWBYTE только-только переходит на высокий уровень; просто в этом случае перенос данных заканчивается чуть раньше. Более интересен случай, когда сигнал SCLK приходит чуть позже, в результате чего сигнал NEWBYTE, переходящий на высокий уровень, оказывается пропущенным и обнаруживается на один период сигнала SCLK позднее. В этом. случае временнь/е диафаммы имеют вид, указанный на рис. 8.108. На этих временньгх диафаммах изображен случай, в котором сигнал NEWBYTE переходит на высокий уровень примерно в то же время, когда поступает фронт сигнала SCLK, точнее - перед приходом фронта сигнала SCLK на расстоянии, меньшем времени t триггера FF1. Таким образом, триггер FF1 может не увидеть , что сигнал NEWBYTE имеет высокий уровень, либо выход триггера может стать метастабильным и единичное значение сигнала NEWBYTE будет надежно зафиксировано спустя лишь один период сигнала SCLK. После этого только через два периода сигнала SCLK по фронту этого сигнала произойдет зафузка значений сигналов с шины SBYTE в регистр SREG. При таком взаимном расположении сигналов по времени возникают неприятности, потому что к моменту зафузки значения сигналов на шине SBYTE уже изменились и выражают собой следующий принятый байт. Кроме того, сигнал SLOAD может иметь единичное значение в то время, когда приходит импульс SYNC, соответствующий следующему принятому байту, и чуть позднее. Но тогда на обоих входах защелки S и R одновременно действуют сигналы активного уровня, и если они снимаются одновременно, то выход защелки может войти в метастабильное состояние. Если же сигнал сброса R действует дольше, как это показано на временньгх диафаммах, то защелка останется в нулевом состоянии, и следующий принятый байт вообще не будет обнаружен и не будет передан той части интерфейса, которая работает по тактовому сигналу SCLK. Следовательно, нам необходимо более внимательно проанализировать временнь/е диафаммы в случае максимальной задержки и решить, будет ли синхронизирующее устройство функционировать надлежащим образом. Начальной точкой в нашем анализе схемы SCTRL будет указанный на рис. 8.108 момент времени start йт зафужается в регистр HREG по фронту сигнала RCLK в конце импульса SYNC. Процедура заканчивается в момент времени t, когда значения сигналов с шины SBYTE зафужаются в регистр SREG по фронту сигнала SCLK. Максимальная задержка между этими двумя моментами времени, которую мы назовем t, равна сумме следующих составляющих: - jLK Минус один период сигнала RCLK, расстояние между моментом t и предшествующим фронтом этого сигнала, по которому сигнал SYNC принял единичное значение. Это число отрицательно, поскольку сигнал SYNC возникает на один период тактового сигнала раньше того момента, когда фактически происходит зафузка в регистр HREG. Максимальная задержка в триггере от входа CLK до выхода Q. Предполагается, что сигнал SYNC является выходным сигналом триггера, переключающегося по сигналу RCLK. Тогда величина t - это интервал времени между фронтом сигнала RCLK и моментом, когда возникает сигнал SYNC. Максимальная задержка в SR-защелке на рис. 8.106 от входа S до выхода Q. Это задержка, с которой появляется сигнал NEWBYTE. t Время установления триггера FF1 на рис. 8.106. Необходимо, чтобы сигнал NEWBYTE принимал единичное значение к началу этого интервала времени или до него. Только тогда гарантируется обнаружение. ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |