(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

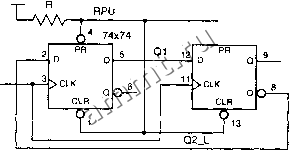

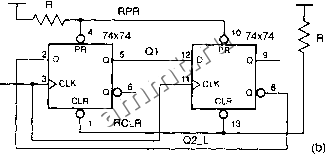

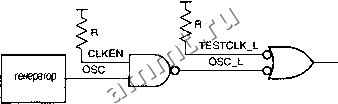

Читальный зал --> Программные средства foundation + 5В CLOCK 74x74  + 5В CLOCK + 5В  Рис. 11.1. Триггеры с резисторами, подключенными между шиной питания и неиспользуемыми входами: (а) не тестируемая схема, (Ь) тестируемая схема Генерирование тактового сигнала. Тестер должен иметь возможность вырабатывать свой собственный тактовый сигнал, не задевая тактовых сигналов, имеющихся на плате. Обычно по нескольким причинам требуется, чтобы тестер подменял тактовый сигнал, имеющийся на плате: скорость, с которой могут подаваться проверочные векторы, ограничена; необходимо дополнительное время, чтобы принудительно задаваемые сигналы приняли установившиеся значения; а иногда необходимо остановить тактовый сигнал. Однако принудительное задание тактового сигнала совершенно недопустимо. В принудительно задаваемом сигнале может быть звон , и такой сигнал может несколько раз перейти с низкого уровня на высокий и обратно перед тем, как примет установившееся значение, определяемое тестером. Поскольку при внутрисхемном тестировании имеется возможность подать на входы регистров и триггеров сигналы установки в единимое состояние и сброса, можно подумать, что никакой проблемы не существует. Однако, на рис. 11.1(a) показан классический случай, когда схема (счетчик, считающий в коде Грея) не может быть инищ1ализирована, так как состояние триггера не предсказуемо, когда сигналы на входах PR и CLR одновременно переходят на неактивный уровень На рис. 11.1(b) показано, как правильно решается проблема установки в единичное состояние и сброса Такие переходы в тактовом сигнале могут приводить к нежелательным изменениям состояния. На рис. 11.2 показана рекомендуемая схема источника тактового сигнала. Чтобы ввести собственный тактовый сигнал, тестер устанавливает на входе CLKEN низкий уровень и подает свой тактовый сигнал на вход TESTCLK L. Поскольку никакие выходы вентилей тестером не преодолеваются, мы получаем чистый сигнал CLOCK. Вообще, из-за недопустимости появления паразитных выбросов в сигнале, который используется в качестве сигнала на тактовом входе или на каком-либо асинхронном входе, тестер не должен принудительно задавать такой сигнал; с этими сигналами следует обращаться так, как показано на рис. 11.2. Это еще одна причина, по которой желательно, чтобы в синхронной системе был один тактовый сигнал. +5 в  CLOCK Рис. 11.2. Схема источника тактового сигнала, позйо/.ч О- (Зя тестеру аюсу-ратно подменить системный тактовый сигна Заземленные входы. В общем случае непосредственное заземление не следует использовать в качестве источника логического 0. Внутрисхемный тестер может принудительно задавать значения большинства сигналов, но он не может изменить значение сигнала на заземленном входе. Поэтому входы, на которые должен быть постоянно подан логический О во время нормальной работы схемы, нужно заземлять через резистор, что позвол ит тестеру устанавливать на этих входах логическую 1, если это потребуется при тестировании. Посмотрите, например, что произошло бы при формировании с помощью ПЛУ GAL16 V8 требуемой совокупности тактовых сигналов из сигнала задающего генератора, как мы делали это в профамме на языке ABEL (табл. 8.26). Если не учитывать потребности тестирования, то мы могли бы непосредственно соединить с землей вывод 11 ИС 16V8, низкий уровень сигнала на котором является глобальным разрешением выхода. Однако этот вывод следует заземлить через резистор, чтобы тестер мог переводить выходы ПЛУ в фетье состояние и сам задавать тактовые сигналы P1 L-P6 L. Хотя теоретически тестер мог бы принудительно устанавливать значения этих сигналов, делать этого не следует, если они используются в качестве тактовых сигналов. Шинные формирователи. Для того чтобы тестер мог подавать сигналы на шину и при этом не преодолевать значения сигналов, вырабатываемых другими источниками, нужно отключать эти источники. Это означает, что должна существовать возможность переводить все выходы схем, подключенные к шине, в третье состояние, чтобы тестер выдавал сигналы на плавающую шину. При этом уменьшается электрическая нагрузка как на тестер, так и на многоразрядные источники сигналов (например, на ИС 74x244), которые в противном случае могут перефеваться и выходить из строя при одновременном принудительном задании на их выходах значений, противоположных тем, какие вырабатываются этими микросхемами. 11.2.3. Методы сканирования Внутрисхемное тестирование хорошо работает до определенных пределов. Оно не годится для заказных СБИС и специализированных ИС, потому что внутренние сигналы в них просто недоступны. Даже в схемах, собранных на печатных платах, методы плотной упаковки типа поверхностного монтажа значительно затрудняют создание на плате конфольных точек для каждого сигнала. В результате, для обеспечения управляемости и наблюдаемости во все большем числе проектов используют методы сканирования . Метод сканирования {scan method) предполагает, что для задания внутренних сигналов в схеме и для наблюдения за ними используется лишь небольшое число контрольных точек. Метод сканирования по заданному пути {scan-path method) основан на предположении, что любая цифровая схема представляет собой комбинацию триггеров или других запоминающих элементов, объединенных комбинационной логикой. С помощью этого метода осуществляется управление и наблюдение за состоянием запоминающих элементов. Метод сканирования по заданному пути предполагает наличие двух режимов работы: режима нормальной работы и режима сканирования {scan mode), при котором все запоминающие элементы входят в состав гигантского регистра сдвига. В режиме сканирования состояние п запоминающих элементов схемы может быть прочитано за п сдвигов (наблюдаемость). За то же время все элементы можно установить в новое состояние (управляемость). На рис. 11.3 показана схема, в которой применен метод сканирования по заданному пути. В этой схеме каждый запоминающий элемент является сканируемым триггером (см. раздел 7.2.7), информацию в который можно зафузить от одного из двух источников. Сигналом, поданным на вход разрешения тестирования ТЕ, выбирается источник данных: обычные данные (поступающие на вход D) или проверочные данные (поступающие на вход Т). Для образования пути сканирования, показанного синим цветом, вход Т каждого триггера соединен с выходом предыдущего триггера, в результате чего возникает последовательная цепочка. Удерживая в течение 11 периодов тактового сигнала активный уровень на входе ENSCAN, тестер может увидеть текущие состояния триггеров и зафузить новые состояния. Инженеру, занимающемуся тестированием, остается лишь написать тестовые последовательности для отдельных комбинационных логических блоков, которые становятся, таким образом, полностью управляемыми и наблюдаемыми со стороны внешних входов и выходов посредством сканирования по заданному пути. ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |