(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

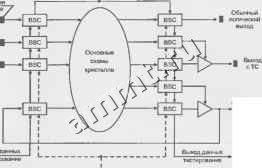

Читальный зал --> База цифровых устройств Логические входы  Двунаправленный выход

Вход От предыдущей D Q С 1 К следующей D Q С 2 Выход Сдвиг Захват ОБновлвние Рис. 8.24. Структура аппврвтных средств интерфейсе JTAG (а) и схема ячейки периферийного сканирования (б) Проверка работы самих микросхем состоит в задании для них входного воз-цействия и наблюдения за полуюнным результатом, проверка исправности монтажа микросхем на плате осушествляется, напр тмер, при взаимодействии двух микросхем, имеющих JTAG интерфейс. В этом случае тестирующая информация вводится в выходные ячейки одной микросхемы, а затем 442 ф1фровая схемотехшка переписывается во входные ячейки другой. При исправности всех межсоединений принятая информация идентична введенной. Порт тестирования ПТ (ТАР, Test Access Port) - это 4 (иногда 5) специально выделенных выводов микросхемы. Функциональное назначение этих линий: TDI (вход тестовых данных) - вход последовательных данных периферийного сканирования. Комвнды и данные вдвигаются е микросхему с этого вывода по переднему фронту сигнала ТСК; ТОО (выход тестовых данных) - выход последовательных данных. Команды и данные выдвигаются из микросхемы с этого вывода по заднему фронту сигнала ТСК: тек (вход тестового тактирования) - тактирует работу встроенного автомата управления периферийным сканированием. Максимальная частота сканирования периферийных ячеек равна 8 МГц, TMS (вход управления тестированием) - обеспечивает выбор режима тестирования. В некоторых случаях к перечисленным сигналам добавляется сигнал TRST для инициализации порта тестирования, что необязательно, т. к. инициализация возможна путем подачи соответствующей последовательности сигналов на входТМБ. Работа средств обеспечения интерфейса JTAG подчиняется сигналам автомата управления, встроенного в микросхему. Состояния автомата определяются сигналами TDI и TMS порта тестирования. Определенное сочетание сигналов TMS и ТСК обеспечивает ввод команды для автомата и ее исполнение Порядок операций при периферийном сканировании: загрузка кода команды, загрузка данных, исполнение команды, считывание результата. Подробнее о работе средств управления интерфейсом JTAG говорится, например, в работе [30]. С помошью расширения возможностей интер( сйса JTAG можно производить также реконфигурацию микросхем непосредственно в системе, без извлечения микросхем из устройства. Программирование в системе Реконфигурации (программирование) в системе - одно важнейших лос тоинств СБИС ПЛ, позволяющее легко производить изменения в логике их работы. Потребности в изменениях возникают как для устранения не выявленных при первоначальном тестировании ошибок, так и при модериизашш системы (Upgrade). Свойство программируемости непосредственно в системе обозначается аббревиатурой ISP (In System Programmable). Создание хорошо приспособленной к программированию в системе БИС/СБИС предъявляет определенные требования к ее архитектуре и программному обеспечению средств проектирования. Задача изменения функционирования БИС/СБИС легче решается при использовании в ней мелкозернистых логических блоков {см. §8.2), наличии схем разделения термов в CPLD. управлений инверсиями, гибких вариантов установок и тактирования триггеров и т. д. Возможности программирования в системе растут, если при проектировании часть функциональных возможностей СБИС ПЛ оставлять свободной, имея в виду упрощение изменений проекта в будущем. При этом рекомендуется иметь запас по скорости, фyнкцuonaJшым возможностям и ресурсам межсоединений Если первоначальным вариантом проекта заняты более 90% емкости микросхемы и скорость ее работы близка к пределу, то для облегчения последующих изменений целесообразно подумать о применении больщей !!о уровню интеграции или более быстродействующей микросхемы, поскольку ожидать успешмоиэ апгрейда без запасов ресурсов рискованно. Следует иметь в вицу, что при реконфигурации в системе должно сохраняться назначение внешних выводов, поскольку иначе потребуется изменить монтаж печатных плат. Требования к числу допустимых для микросхемы циклов репрограммирования Эти требования зависят от решаемых задач. Для отработки прототипа, работа которого в дальнейшем будет неизменной, достаточным может быть число циклов репрограммирования порядка нескольких десятков, что обеспечивается даже схемами с УФ-стиранием данных. Для многих других приме-иетш число допустимых циклов репрофаммирования должно быть сушественно большим или даже практически неограниченным. Настройка микросхем программируемой логики Настройка на требуемый алгоритм функционирования производится с помошью программаторов (например, для PLD) либо непосредствешю в системе, что рассмотрено выше. Последнее характерно для СБИС ПЛ с триггерной памятью конфигурации. Средства конфигурирования СБИС ПЛ с триггерной теневой памятью позволяют загружать ее от внешней памяти различными способами. Данные для конфигурирования мотут поступать от разных источников (компьютера, ПЗУ, других СБИС ПЛ), форма их представления может быть последовательной или параллельной, роль конфигурируемой СБИС может быть активной или пассивной. В результате возникают несколько возможных режимов конфигурирования СБИС ПЛ. имеющие интерфейс JTAG, мотут конфигурироваться с его использованием (расширенный интерфейс JTAG). Для иллюстрации общих положений, касающихся конфигурирования СБИС ПЛ, рассмотрим несколько подробнее режимы конфигурирования на примере FPGA семейства ХС4000 [ЗО]. Микросхемы семейства ХС4000 используют по несколько сотен битов конфигурации на каждый логический блок и ею межсоединения. Каждый бит

ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |