(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

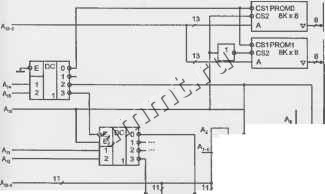

Читальный зал --> База цифровых устройств Глава S ВУ - линейную селекцию. Пусть для ПЗУ отведено 16К адресов в начале АП, адреса ВУ занимают третью четверть АП, а адреса ОЗУ занимают последние 8К адресного пространства. Примем, что в системе имеется 5 ВУ, каждое из которьк имеет 4 внутренних регистра со своими адресами, а в качестве ОЗУ используется триггерное тактируемое ЗУ. Распределение АП показано на рис. 5.15, а. Область адресов ВУ Рис. 5.15. Пример распределения адресного пространства между модулями памяти и внешними устройствами (а) и схема адресации модулей памяти и внешних устройств (б) ЕОООН  от МП

Пусть ПЗУ строится на микросхемах с организацией 8Кх8, а ОЗУ на микросхемах 2Кх8. Имея в виду байтовую организацию модуля памяти, видим, что каждая микросхема играет роль субмодудя (не нуждается в нарашивании разрядности хранимых слов). Для адресации ВУ используем младшие разряды шины адреса, число которых определяется как N -и 2, где N - число ВУ, а две линии нужны для адресации их внутренних регистров. Таблица S.6

Схема адресации, соответствующая таблице адресов (табл. 5.6), цривсдсиа иа рис. 5-15, б. Депшфратор DC1 делит АП на четыре части, его выходы разрешают работу тем объектам адресации, которые расположены в соответствующей четверти АП. Линия А13 разрешает работу микросхемы PROMO в первой половине первой четверти АП при нулевом состоянии и работу микросхемы PROM1 - при единичном. Линии A2...At использованы для линейной селекции внешних устройств, а линии А12 и Ап декодируются дешифратором DC2, для разрешения работы микросхемам SRAM3...SRAM0 в их зонах адресов. Символом X обозначены безразличные состояния адресных разрядов, а буквой d - разряды, декодируемые на кристалле , т. е. входящие в состав адресных входов самих микросхем памяти или адресных линии внутренних регистров ВУ. Пример 4 С целью упрощения схем декодирования и при наличии лишнего адресного пространства можно применить неабсолютную адресацию, при которой каждому объекту адресации присваивается не один-единственный адрес, а группа адресов (некоторая зона АП) Пусгь, например, в АП емкостью 64К требуется разместить всего два субмодуля памяти по 8К адресов в каждом. При абсолютной адресации (рис. 5.16, й) на адресные входы самих ИС памяти поступают 13 младших разрядов адреса для адресации 8К ячеек субмодуля- Оставшиеся разряды А5-13 поступают на дешифратор, нулевой и единичный выходы которого разрешают работу субмодудеи СМ 1 и СМ2. Остальные выходы дешифратора могут быть использованы для подключения других объектов адресации в зоне АП, оставшейся свободной (48К). ек вк СуБмодуль 1 Субмодупь 2 Свободная область СМ1 ICS Субмодуль 1 Субмодупь 2 А СМ2 Рис. 5.16. Примеры реализации абсолютной (а) и неабсолютной (б) адресации субмодулей памяти При неабсодютной адресации линии адреса а12-0 по-прежнему подаются на адресные входы ИС, а для выбора одной из них используется линия А]5. Линии Ai4 и Af3 не используются вообще, их состояния безраз;п1чн1,1. Схема адресации (рис. 5.16, ф упрощается, вместо депшфратора 3 на 8 нужен только инвертор. Платой за это является занятие двумя субмодудями по 8К всего АП. Действительно, все адреса вида OXXdd...d принадлежат субмодулю CMI, а это соответствует верхним 32К АП. Все адреса вида lXXdd...d принадлежат субмодулю СМ2 и занимают 32К в нижней части АП. Неабсолютная адресация - достаточно гибкий подход к построению схем декодирования адреса. Для адресации объекта можно использовать более пли менее широкую зону АП, выбирая при необходимости компромисс между крайними решениями, показашш1ми на рис, 5,16.

ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |