(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

Читальный зал --> Полупроводниковая схемотехнология Рис. 19.22. Схема определения равнозначности для двух N-разрядных чисел. ваются поразрядно с помощью нескольких схем равнозначности, выходы которых подключены к элементу И, как показано на рис. 19.22. Шы ИС 2x6 входов: DM 8131 (ТТЛ); изготовитель-фирма National. 2x8 входов: AM 25LS2521 (ТТЛ); изготовитель-фирма AMD. Универсальными являются такие компараторы, которые помимо констатации равенства двух чисел могут установить, какое из них больше. Такие схемы называются компараторами со сравнением величин (Magnitude Comparator) или просто компараторами. Чтобы провести сравнение величин, нужно знать, в каком коде представлены числа. В дальнейшем мы будем исходить из того, что числа заданы в двоичном коде, т.е. A = a ,.2- +а г2-... + + a2 + ао-2°. Простейшая задача состоит в сравнении двух одноразрядных чисел. При составлении логической функции компаратора будем исходить из таблицы переключений 19.6, непосредственно из которой легко по- ч Таблица 19.6 Таблица переключений одноразрядного компаратора

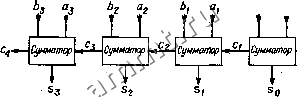

Уа.Ь У-Уа>Ь Рис. 19.23. Функциональная схема одноразрядного компаратора. лучить изображенную на рис. 19.23 схему компаратора. Для сравнения многоразрядных двоичных чисел используется следующий алгоритм. Сначала сравниваются значения старших разрядов. Если они различны, то эти разряды и определяют результат сравнения. Если они равны, то необходимо сравнить следующие за ними более младшие разряды, и т.д. Таким образом, для каждого разряда можно использовать схему, представленную на рис. 19.23, передавая через мультиплексор на выход результат сравнения самых старших из несовпадающих разрядов. Подобные схемы для сравнения 4- и 5-разрядных чисел выпускаются в интегральном исполнении: SN 7485 (ТТЛ); МС 10166 (ЭСЛ); МС 14585 (КМОП). , Эти схемы можно наращивать как последовательно, так и параллельно. На рис. 19.24 показано последовательное соединение компараторов для увеличения разрядности сравниваемых чисел. Есж старшие три разряда чисел А vi В равны, то результат сравнения определяется сигналами на выходах компаратора К, поскольку они подключены к входам младшего разряда компаратора Xj. ♦ bjQj biOz b,a, Ьдйд Катара тор Кг А<В А=В А>В ЬзОз Ьа Ь,а, ЬдЩ Компаратор К) А<В А=В А>В Рис. 19.24. Последовательное соединение компараторов для увеличения разрядности сравниваемых чисел. 15 14 13 °1г °11 Ою Од о& ? е Os °4 Оз в? Oi о Компаратор Кл Компаратор Кя а<в ав J8 J j5J4 ЬзаЬгагЬ/ОЬдОд Компаратор Ks а<в а=в а>в ~т~гг Иа<В УАВ Уа>в Рис. 19.25. Параллельное соединение компараторов. Компаратор Kg КомпаратоК] При сравнении чисел со значительным количеством разрядов целесообразнее использовать параллельное соединение компараторов, показанное на рис. 19.25, так как оно обеспечивает меньшее время задержки. 19.5. СУММАТОРЫ 19.5.1. ПОЛУСУММАТОР Сумматором называется схема, предназначенная для сложения двоичных чисел. Ниже мы рассмотрим сумматоры для чисел, представленных в двоичном коде. Простейшей задачей является сложение двух одноразрядных чисел. Для того чтобы разработать логическую схему, в первую очередь следует рассмотреть все возможные сочетания входных переменных, на основании чего можно будет составить таблицу переключений. При сложении двух одноразрядных чисел А и В могут наблюдаться следующие комбинации: Если А и В равны единице, происходит перенос в следующий (более старший) разряд. Следовательно, такой сумматор должен иметь два выхода, а именно один для формирования части суммы, относящейся к данному разряду, и еще один j-для переноса в следующий разряд. Представляя числа А а В логическими переменными а и Ьц, можно получить таблицу переключений 19.7, где Cj-сигнал переноса, Sq-сумма. Составляя дизъюнктивную нормальную форму, получаем следующие булевы функции: Cl = афо, So = dobo + афо = ао© Последовательно, перенос происходит с помощью функции И, а сумма-функции неравнозначности (ИСКЛЮЧАЮЩЕЕ ИЛИ). Схема, реализующая обе указанные функции, называется полусумматором; она показана на рис. 19.26. Таблица 19.7 Таблица переключений полусумматора 0-1-0 = 0, 0-1-1 = 1, 1 + 0 = 1, 1 + 1 = 10. Рис. 19.26. Схема полусумматора. 1> Рис. 19.27. Схема полного сумматора. с, + , = 0,6, + oic, + bic, 19.5.2. ПОЛНЫЙ СУММАТОР Если складываются два многоразрядных двоичных числа, полусумматор можно использовать только для одного младшего разряда. Во всех остальных разрядах складываются не два, а три числа, поскольку может произойти перенос со следующего за ним младшего разряда. Таким образом, в общем случае для каждого разряда необходима логическая схема с тремя входами а,-, Ь,-, с,- и двумя выходами Sj и с, + 1. Такая схема и называется полным сумматором. Ее можно реализовать, например, с помощью двух полусумматоров, как показано на рис. 19.27. Здесь приведена таблица 19.8 переключений такой схемы. Для сложения двух многоразрядных двоичных чисел на каждый разряд необходим один полный сумматор. Только в младшем разряде можно обойтись полусумматором. На рис. 19.28 приведена схема, предназначенная для сложения двух четырехразрядных чисел а w. В. Эта схема Таблица Ш Таблица переключений полного сумматора

выпускается в интегральном исполнении. В ее младшем разряде также используется полный сумматор, чтобы иметь возможность наращивания разрядности схемы (SN 74LS83). 19.5.3. СУММАТОРЫ ПЕРЕНОСОМ С ПАРАЛЛЕЛЬНЫМ Время выполнения операции в сумматоре на рис. 19.28 намного больше времени сложения в одноразрядном сумматоре. Действительно, сигнал переноса только тогда сможет прикять истинное значение, когда перед этим будет установлено правильное значение переноса с3. Такой порядок выполнения операций называется последовательным переносом (Ripple Carry). Чтобы уменьшить время операции сложения многоразрядных чисел, можно использовать схемы параллельного переноса (Carry look-ahead). При этом все сигналы переноса вычисляются непосредственно по значе!ниям входных переменных. Согласно таблице переключений 19.8, в общем случае для сигнала переноса любого i-ro разряда справедливо следующее соотношение: с,+ 1 = аД. + (а bi)c, 9t Pi (19.1)  Рис. 19.28. Четырехразрад-ный сумматор с последовательным переносом.

ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||