(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

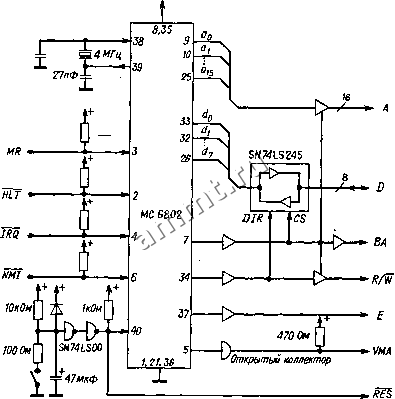

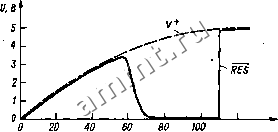

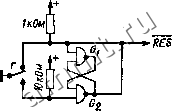

Читальный зал --> Полупроводниковая схемотехнология R/W VMA EX tal X tal IRQ MNI RES; Read/Write, тристабильное переключение запись-считывание . Valid Memory Address. Высокий уровень показывает, что выдан действительный адрес. Bus Available. Высокий уровень на этом выходе показывает, что микропроцессор находится в состоянии останова (HALT) или ожидания (WAIT), а тристабильные выходы-в отключенном состоянии, характеризующемся высоким выходным сопротивлением. Enable (Ф2). Выдача тактовых импульсов системы. Вход для внешних тактовых импульсов. Для входа Е частота тактовых импульсов системы в 4 раза меньше частоты приложенных сигналов. Служит вместе со входом ЕХ tal для подключения внешнего кварцевого резонатора к внутреннему тактовому генератору. Останов. Появление низкого уровня останавливает процессор. Все тристабильные выходы находятся в отключенном состоянии. Кроме того, ВА = 1 W VMA = 0. Memory Ready. Низкий уровень блокирует тактовые импульсы и переводит переменную Е в единичное состояние. При этом становится возможным обмен данными с медленной памятью. Максимальное гарантируется время ожидания составляет в этом случае 10 мкс. Входы прерываний. RAM-Enable. Низкий уровень подключает внутреннее ОЗУ. Как было показано на рис. 21.1, выводы шины данных микро-ЭВМ соединены параллельно с.выводами ЦПЭ, запоминающих и периферийных устройств. Такая структура называется магистральной или шинной (BUS). Ясно, что данные всегда необходимо передать на шину только для одногоабонента. Для выбора этого абонента служит шина адреса. По шине управления передаются дополнительные сигналы для задания направления передачи данных и синхронизации. К выходу микропроцессора можно подключить до 10 входов МОП-схем или 5 входов маломощных схем с диодами Шоттки. В связи с этим для создания сложных систем ко всем выходам необходимо подключить буферные усилители. На рис. 21.13 показано, как они подключаются к микропроцессору. Для двунаправленной шины данных необходимо использовать двунаправленные буферные усилители. Эти усилители соединяют параллельно и встречно, причем они имеют выходы с тремя состояниями, которые подключаются попеременно с помощью переключателя направления DIR. Для переключения используется сигнал R/W микропроцессора. Вывод выбора кристалла буферного усилителя CS (Chip-Select) соединен с выходом ВА микропроцессора. Благодаря этому шина данных отключается, есж микропроцессор остановлен. Такой режим работы необходим для прямого доступа к памяти. Для этой цели к шине данных и выходу R/W тоже подключен буферный усилитель, имеющий выход с тремя состояниями. В микропроцессорной технике наиболее применимы следующие типы буферных усилителей, имеющих выход с тремя состояниями и вьшолненных на базе IfES EUal Vban i Xtal\ E RE I R/Wo d2 dy di ds Ф, oe Оц а,з 1 nnnnnnnnnnnnn П П П n n П ut Э 38 37 3$ 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21 MC 6602 e 7 8 9 10 11 12 13 U 15 IS 17 18 19 20 -tr-D-U U Ц-UUUUUUUUU U Ц U Ц U-U U U-U U Ц-UUUUUUUUU J. \ MR \ VMA \ BA V* oj a, 05 a, oj og a,o a Рис. 21.12. Выводы микропро- НГГ Ш NMI цессора типа МС 6802. маломощных ТТЛ-схем с диодами Шоттки: ; Однонаправленные 6 бит: SN74LS367 (Texas Instr.) 8 бит: SN74LS244 (Texas Instr.) 8 бит: F74LS541 (Fairchild) Двунаправленные SN74LS245 (Texas Instr.) Установка в исходное состояние Во многих случаях требуется, чтобы при включении напряжения питания автоматически происходил сброс. Для этой цели служит КС-цепь на входе RES, соединенная с двумя инверторами (рис. 21.13). Из рис. 21.14, на котором изображена кривая изменения напряжения, видно, что в интервале времени 70-110 мс после + 5В 27 пФ  Рис. 21.13. Подключение микропроцессора МС 6802 к шинам адреса, данных и управления.  т г,мс Рис. 21.14. Временная диаграмма напряжения питания и напряжения сброса при включении. Гмва 21 220Щ 220 Ом 111  Рис. 21.15. Формирование сигнала сброса без помехи при включении. включения производится сброс. Когда сигнал сброса исчезает, напряжение питания достигает значения, соответствующего номинальному режиму микропроцессора. Сразу после включения сигнал сброса нарастает вместе с напряжением питания, т.е. вентиль закрыт вследствие низкого напряжения питания. Такое возрастание напряжения может помешать работе схемы. Особенно это проявляется в тех случаях, когда система содержит ОЗУ, выполненное по КМОП-технологии и эксплуатируемое как микромощная память с резервным источником питания. Как мы увидим позже, при этом сигнал сброса должен быть равен нулю до тех пор, пока микро-ЭВМ не восстановит полностью свою работоспособность, поскольку в противном случае может произойти потеря данных. Это условие может быть выполнено, например, с помощью схемы сброса, приведенной на рис. 21.15. Нормально-замкнутый контакт г реле R блокирует сигнал сброса RES путем подачи нулевого потенциала, пока напряжение питания V* т превысит значения, равного 4,75 В. При этом Л5-триггеры Gj, Gj служат для демпфирования контактов реле в соответствии с методом, описанным в разд. 20.6.1. На рис. 21.6 было показано, что в области памяти, начиная с ячеек FFF8 до FFFF, записываются начальные адреса прерывающих программ. Если в этой области располагается ОЗУ, то туда можно загружать адреса, например программы монитора. Но в начале программы монитора должен быть установлен адрес точки повторного пуска FFFE/FFFF. На рис. 21.16 показана возможность извлечения содержимого обеих ячеек памяти, расположенных в области ОЗУ, и замены их переключателем. Если микропроцессор вьщает адреса FFFE и FFFF, а также сигнал считывания, то провод VMA через открытый коллектор элемента соединяется с нулем. Для этого необходимо на плате ЦПЭ в качестве формирователя провода VMA использовать элемент с открытым коллектором (рис. 21.13). Поскольку VMA = О, то адресация производится не к памяти, т.е. не к содержимому ячейки FFFE и FFFF. Вместо этого состояние переключателя подается через буферный усилитель с тремя состояниями на шину данных, а именно: старший байт по адресу FFFE (ад = 0), а младший байт по адресу FFFF (aj, = 1). Если использовать совокупность переключателей, формирующих двоичный код, то можно задавать адрес повторного пуска непосредственно в шестнадцатеричном коде. О о Открытый коллектор vma 6, -гче. Старший байт ЮкО МладшийУГ 9 байт 1 8х Рис. 21.16. Схема повторного пуска с регулируемым начальным адресом. 21.6.2. ПЛАТА ОЗУ В табл. 21.12 перечислены характеристики ОЗУ, которые являются наиболее подходящими для работы с микро-ЭВМ.

ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |