(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

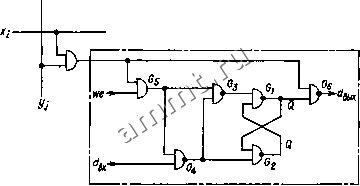

Читальный зал --> Полупроводниковая схемотехнология

Дешифратор стОАбирв Рис. 9.38. Внутреннее строение ОЗУ емкостью 16 бит. Рис. 9.39. Логическая схема замещения для одной ячейки ОЗУ.  дой ячейки памяти к внутренним шинам 4. вш и we представлена на рис. 9.39. Запись информации в ячейку памяти происходит только тогда, когда будет выбран ее адрес и, кроме того, we = I. Эта логическая связь осуществляется элементом G5. Содержимое ячейки поступит на выход, если на ее вертикальную и горизонтальную шины выбора адреса подан единичный сиг- нал, Х = 1, У1= 1. Эту связь осуществляет элемент G, который имеет выход с открытым коллектором. Если задан адрес не этой, а другой ячейки, выходной транзистор заперт. Выходы всех ячеек соединяются между собой, реализуя функцию монтажное И , и через показанный на рис. 9.38 трехстабильный элемент подключаются к выходу йвьи- Гмва 9 Для того чтобы в одной микросхеме разместить наибольшее число ячеек, каждую из них следует реализовать как можно более простым способом. Как правило, они состоят из нескольких транзисторов. В простейшем случае можно, однако, убрать триггер, заменив его одним конденсатором. В такой динамической ячейке информация может сохраняться только в течение ограниченного времени. Поэтому необходимо ее обновлять (регенерировать). Как правило, для этого необходимо один раз каждые 2 мс активизировать все вертикальные координатные шины. Одна обшая особенность всех полупроводниковых ОЗУ состоит в том, что при отключении питания теряется записанная в них информация. Поэтому в отличие от ЗУ, использующих принципы ферромагнетизма, они называются также энергозависимыми ОЗУ. Динамические свойства Чтобы обеспечить нормальное функционирование ОЗУ, следует выполнить некоторые временные соотношения между входными сигналами. На рис. 9.40 показана временная диаграмма процесса записи информации. Для предотвращения записи информации в неправильно выбранную ячейку импульс разрешения записи следует подавать вслед за адресом только по истечении определенного времени. Это время называется временем дешифрирования адреса 1а (Address Setup Time). Для того чтобы обеспечивалась надежная запись в выбранную ячейку, длительность импульса разрешения записи не должна быть ниже минимального значения tw (Data Write Time). В случае значительного числа микросхем ОЗУ информация на входе должна сохраняться еще некоторое время tn (Data Hold Time) после окончания импульса записи. Сумма этих времен называется длительностью цикла записи (Write Cycle Time). Процесс чтения информации представлен на рис. 9.41. После установки адреса достоверная информация появится через интервал времени tR. Это время называется временем доступа при чтении (Read Access Time) или просто временем доступа. Параметры некоторых широко распространенных микросхем ОЗУ, выполненных как по биполярной, так и МОП-технологии, приведены в табл. 9.17. CS А CS А

Рис. 9.40. Временная диаграмма процесса записи. -время дешифрирования адреса; ty/-ipoa записи; tjf-время задержки информаш1и. Рис. 9.41. Временная диаграмма процесса чтения. (Сигнал WE = 0; (д-время доступа.) Параметры некоторых распространенных микросхем ОЗУ

9.6.2. ПОСТОЯННЫЕ ЗАПОМИНАЮЩИЕ УСТРОЙСТВА (ПЗУ) Запоминающие устройства, в которых информация записывается при их изготовлении, называют постоянными запоминающими устройствами (Read Only Memory-ROM). Их принципиальная схема представлена на рис. 9.42. Деишфраторы адреса здесь ничем не отличаются от используемых в ОЗУ (рис. 9.38). Запись каждого бита информации производится введением или разрущением контакта между Дешифратор столбцов 0 CS Рис 9,42. Внутреннее строение микросхемы ПЗУ емкостью 16 бит.

ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||