(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

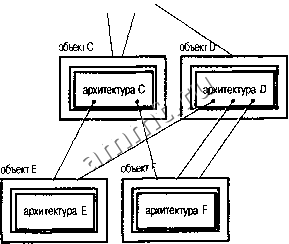

Читальный зал --> Программные средства foundation точностью найти реальные задержки в схеме, обусловленные длиной соединений, величиной нагрузки и другими факторами. Обычно на этом этапе используются те же самые условия тестирования, что и при функциональной верификации, только на данном шаге в эти условия помещается схема, которая в действительности будет построена. Как и в любом другом творческом процессе может случиться так, что после продвижения на два шага вперед, вам приходится делать шаг назад (если не хуже!). Как отмечено на рисунке, при написании программы могут встретиться проблемы, которые заставят вернуться назад и пересмотреть иерархию, и почти наверняка в процессе компиляции и моделирования обнаружатся ошибки, из-за которых вам придется переписать часть программы. Самыми болезненными в ходе выполнения проекта бывают те проблемы, с которыми вы сталкиваетесь при выполнении этапов внутреннего плана. Если, например, результат синтеза не влезает в имеющийся кристалл FPGA или не удовлетворяет временным требованиям, может случиться так, что вы должны будете вернуться назад и пересмотреть сам подход к проекту в целом. Стоит напомнить, что прекрасные программные средства не заменяют все же тщательного продумывания проекта в самом начале. 4.7.2. Структура программы При создании языка VHDL имелось в виду воплотить в нем принципы структурного программирования с заимствованием идей у языков профаммирования Паскаль и Ада. Ключевая идея состояла в том, чтобы задать интерфейс схемного модуля, а его внутреннее устройство скрыть. Таким образом, объект (entity) в языке VHDL - это просто объявление входов и выходов модуля, а архитектура (architecture) - подробное описание внутренней структуры модуля или его поведения. РАБОТАЕТ!? Как разработчик и системщик с многолетним опытом, я всегда думал, что знаю, что имеется в виду, когда кто-то говорите своей схеме: Она работает! . На мой взгляд, это означает, что вы можете пойти в лабораторию, подать питание на макет (и при этом не пойдет дым), нажать кнопку Пуск и с помощью осциллофафа или логического анализатора наблюдать, как ваш макет последовательно вьЕполняет необходимые действия. Но с годами значение слов она работает изменилось, по крайней мере, для некоторых людей. Когда несколько лет назад я перешел на новую работу, я порадовался, услышав, что несколько основных специализированных ИС для нового важного продукта работают . Но позднее (спустя совсем немного времени) я понял, что эти ИС работают только при моделировании и что коллективу, занятому в этом проекте, предстоит еще не раз возвращаться назад и понадобится несколько месяцев напряженного труда для синтеза, подгонки и проверки временных соотношений, прежде чем они смогут заказать опытные образцы. Да, верно: Она работает! . Только это напоминает мне, как мои дети говорят о домашнем задании: Готово! . Рис. 4.51 (а) иллюстрирует этот принцип. Многие разработчики склонны считать обьявление объекта в языке VHDL оболочкой архитектуры, скрывающей детали того, что находиться внутри, но обеспечивающей зацепки для других модулей, использующих данный модуль. Эта идея служит основой иерархического подхода к проектированию систем: архитектура верхнего уровня может использовать (или обрабатывать ) другие объекты, оставляя архитектурные детали объектов нижнего уровня скрытыми от объектов более высокого уровня. Как показано на рис. 4.51(b), архитектура более высокого уровня может использовать объекты более низкого уровня многократно, и несколько архитектур верхнего уровня могут использовать один и тот же объект более низкого уровня. На рисунке архитектуры В, Е и F являются самостоятельными; они не используют никакие другие объекты. (а) объект (Ь) обьеетА

обьекгВ

Рис. 4.51. Объекты и архитектуры языка VHDL: (а) идея оболочки ; (Ь) иерархическое использование ПИШИТЕ ВСЕ, ЧТО ХОТИТЕ! В действительности, язык VHDL позволяет определять несколько архитектур, объединенных в одном объекте, и предоставляет средства управления конфигурацией, посредством которых можно указывать, какая именно архитектура будет использоваться при очередном запуске компилятора или программы синтеза. Это позволяет опробовать различные архитектурные подходы, не выкидьшая и не пряча другие варианты. Однако в нашем учебнике мы не воспользуемся этой возможностью и не станем ее обсуждать подробнее. В текстовом файле на языке VHDL объявление объекта {entity declaration) и определение архитектуры {architecture definition) разделены, как это сделано на рис. 4.52. В табл. 4.26 в качестве примера приведена очень простая программа на языке VHDL для 2-входового вентиля запрета . В больших проектах объекты и архитектуры иногда бывают помещены в отдельные файлы, связь между которыми компилятор обнаруживает по их объявленным именам, текстовый файл (например, mydesign vhd) объявление объекта определение архитеюуры Рис. 4.52. Обшяй вид файла программы на языке VHDL Табл. 4.26. Программа на языке VHDL для вентиля запрета entity Inhibit is - also known as BUT-NOT port (X,Y: in BIT; - as in X but not Y Z; out BIT); - (see [Klir, 1972]) end Inhibit; architecture Inhibit arch of Inhibit is begin 1 <= 1 when X=l and Y=0 else 0; end Inhibit arch; Как и в других языках профаммирования, в языке VHDL пробелы и переходы с одной строки на другую в общем случае игнорируются, и для удобства чтения их можно вставлять как угодно. Комментарии {comments) начинаются с двух дефисов (-) и заканчиваются концом строки. В языке VHDL определено много специальных строк символов, называемых зарезервированными словами {reserved words) или ключевыми словами {keywords). В приведенном примере имеется несколько ключевых слов: entity, port, is, in, out, end, architecture, begin, when, else и not. Определяемые пользователем идентификаторы {identifiers) начинаются с буквы и содержат буквы, цифры и подчеркивания. (Символ подчеркивания не может следовать за другим символом подчеркивания и не может быть последним символом идентификатора.) В данном примере идентификаторами являются Inhibit, X, У, BIT, Z и Inhibit arch. BIT - это встроенный идентификатор предопределенного типа; он не считается зарезервированным словом, так как его можно переопределять. Зарезервированные слова и идентификаторы не чувствительны крегистру. ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |

|||||||||||||||||||||||||||