(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

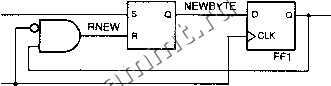

Читальный зал --> Программные средства foundation SYNC SCLK  SLOAD Рис. 8.109. Схема SCTRL, вырабатывающая сигнал SLOAD на половине периода тактового сигнала Для правильной работы каждой из рассмотренных схем синхронизации требуется, чтобы частота тактового сигнала находилась в определенном диапазоне значений; у каждой схемы этот диапазон шой. Это необходимо учитывать при тестировании, когда тактовые сигналы обычно бывают более медленными, а также при модернизации, связанной с увеличением одной или обеих тактовых частот. В случае интерфейса сети Ethernet, например, не предполагается изменение стандартной частоты 100 Мбит/с, но частота тактового сигнала в шине PCI может быть повышена и стать равной не 33 МГц, а 66 МГц. Проблемы, возникающие в связи с изменением частоты тактового сигнала, могут быть довольно тонкими. Чтобы получить представление о том, что может нарушиться, полезно посмотреть, как будет работать (или не работать!) синхронизирующее устройство, если одну из тактовых частот изменить в 10 раз или более. Что произойдет, например, с временными диафаммами, представленными на рис. 8.107, если мы изменим частоту сигнала RCLK и сделаем ее равной не 100 МГц, а 10 МГц? На первый взгляд кажется, что все бдет хорошо, поскольку теперь байт поступает раз в 800 не и имеется много больше времени для переноса его в часть схемы, работаюшую с тактовым сигналом SCLK. Верно: неравенства (8.1) и (8.2) в данном случае удовлетворяются с много ббльшим запасом. Однако неравенство (8.3) более не выполняется, если только мы не уменьшим значение п до нуля! Это можно было бы исправить, вырабатывая сигнал SYNC на один такт позднее сигнала RCLK, нежели это показано на рис. 8.107. Но даже при таком изменении некоторая проблема все же остается. На рис. 8.110 приведены новые временные диаграммы, в том числе для вырабатываемого позднее сигнала SYNC. Проблема заключается в том, что теперь длительность импульса SYNC равна ШОнс. Как и ранее, сигнал NB/VBYTE (на выходе SR-защел- 3. Интервал времени, в пределах которого сигнал SCLK имеет низкий уровень, достаточно велик для того, чтобы был выработан импульс сброса в точке RNEW, удовлетворяющий требованию SR-защелки в отношении минимальной длительности импульса. Заметьте, что при выполнении этих условий правильность работы схемы зависит от коэффициента заполнения сигнала SCLK. Если сигнал SCLK является относительно медленным и его коэффициент заполнения близок к 50%, то данная схема прекрасно работает Но если частота сигнала SCLK слишшм велика, либо его коэффициент заполнения очень мал, очень велик или непредсказуем, то необходимо воспользоваться первоначальной конструкцией. RCtK SYNC SCLK SBYTE NEWBYTE SM SMI SLOAD 100 hc 30нс установившиеся Рис. 8.110. Временные диаграммы для синхронизирующего устройства в случае медленного тактового сигнала (с частотой 10 МГц) Решение этой проблемы состоит в том, чтобы реагировать только на нарастающий фронт сигнала SYNC, и тогда схема окажется нечувствительной к длительности импульса SYNC. В общем случае это делается путем замены SR-защелки переключающимся по фронту D-триггером, как показано на рис. 8.11L По нарастающему фронту сигнала SYNC триггер устанавливается в единичное состояние, а сигналом SLOAD, как и ранее, осуществляется асинхронный сброс. SYNC SCLK 4.CLK CLR NEWBYTE О о >CLK SM -. D о >CLK SLOAD Рис. 8.111. Синхронизирующее устройство с обнаружением сигнала SYNC посредством переключения по его фронту Приведенная на рис. 8.1И схема позволяет решить проблему, возникающую при слишком медленном сигнале RCLK, но при этом изменяются также выкладки, приводящие к соотношениям (8.1)-(8.3), результатом чего могут стать временные офаничения в каких-то других местах (см. задачу 8.96). Еще один недостаток последней ки в схеме на рис. 8.106) принимает активное значение по сигналу SYNC и сбрасывается сигналом SLOAD, но когда сигнал SLOAD заканчивается, сигнал SYNC все еще остается на активном уровне, как это видно из новых временных диаграмм. Следовательно, новый байт будег обнаружен и передан далее дважды! схемы состоит в том, что ее нельзя реализовать в типичном ПЛУ, у которого все триггеры переключаются одним и тем же тактовым сигналом; поэтому для обнаружения сигнала SYNC необходимо воспользоваться отдельным триггером. Прочтя почти десять страниц, посвященные анализу всего лишь одного простого примера, вы, по-видимому, получили представление о том, как трудно правильно сконструировать синхронизирующее устройство. Вот несколько правил, которые могут вам помочь: Минимизируйте число подсистем, работающих с различными тактовыми сигналами. Четко определите фаницы между всеми тактовыми сигналам и и в явном виде поместите на этих фаницах синхронизирующие устройства. Обеспечьте для каждого синхронизирующего усфойства достаточное время выхода из метастабильности, чтобы сбои синхронизирующих устройств были редкими и происходили с много меньшей вероятностью, чем возникновение неисправности в других местах. Проанализируйте работу синхронизирующего устройства при различных возможных сдвигах сигналов во времени, в том числе при более быстрых и более медленных тактовых сигналах, которые могут подаваться на схему при моделировании или при модернизации системы. Осуществите моделирование работы системы в широком диапазоне возможных временнь/х соотношений между сигналами. Последнее правило может оказаться ловушкой для тех разработчиков, кто полагается на современные мощные и быстродействующие средства моделирования при поиске своих ошибок. Само по себе моделирование не может избавить от необходимости следования предыдущим четырем правилам. Если игнорировать эти правила, то можно столкнуться с проблемами, которые не обнаруживаются моделированием в типичных случаях, когда перебирается небольшое число вариантов соотношений между сигналами. Из всех цифровых схем синхронизирующие устройства являются такими конструкциями, для которых важнее всего быть правильным по идее ! Обзор литературы По-видимому, первым источником подробных сведений о последовательностных ИС средней степени интефации стал Справочник по применению ТТЛ под редакцией Алфке и Ларсена {The TTL Applications Handbook, edited by Peter Alfke and lb Larsen. Fairchild Semiconductor, 1973). Эта очень полезная и содержательная книга была неоценимым подспорьем для автора и для многих других, чья деятельность на поприще цифрового проектирования начиналась в 70-е годы. В книге Блейксли Цифровое проектирование на основе стандартных МИС и £0 (Thomas R. Blakeslee. Digital Designwith Standard MSI and LSI, second edition. Wiley, 1979) упор был сделан на реализацию комбинационной и последовательностной логики с помощью микросхем большей степени интефации. Книга содержит блестящее изложение вопроса о пространственно-временном обмене, а ее автор был одним из первых, кто ввел представление о микропроцессоре как об универсальной логической схеме . ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |