(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

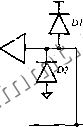

Читальный зал --> Программные средства foundation к другим блокам ввода/вывода к переключающей матрице от макроячейки p-pQ l/O/GTSI I/0/GTS2 I/0/GTS3K. о-> I/0/GTS4 Блок ввода/вывода гclт входной буфер.  выходной Включение подтяжвающе-горисгора -С? 1/0 Программируемое пользователем заземление Управление скоростью изменения сигнала Общие сигналы разрешения выхода Рис. 10.41. Блок ввода/вывода микросхем серии ХС9500 10.5.3. Архитеюура блока ввода/вывода Структура блока ввода/вывода {I/O block, IOB) в ИС семейства ХС9500 показана на рис. 10.41. Имеются семь вариантов выбора сигнала разрешения выхода для выходного буфера с тремя состояниями. Буфер может быть всегда открытым, всегда запертым, его состояние может определяться термом-произведением РТОЕ, поступающим от соответствующей макроячейки, или любым из четырех сигналов общего разрешения выхода. Сигналы общего разрешения выхода могут иметь как высокий активный уровень, так и низкий активный уровень, в зависимости от сигналов на внешних выводах GTS. Блок ввода/вывода микросхем семейства ХС9500 является хорошим примером важной тенденции в архитектуре блоков ввода/вывода микросхем типа CPLD и FPGA: в нем, кроме управления логическими действиями вроде разрешения выхода, имеется возможность изменять многие аналоговые параметры. В блоке ввода/вывода можно изменять значения трех аналоговых параметров: Управление скоростью изменения выходного напряжения. Для того чтобы получать быстродействующее или медленно работающее устройство, можно задавать время нарастания и спада выходных сигналов. Установка наибольшего быстродействия обеспечивает наименьшую возможную задержку распространения, в то время как задание режима медленной работы устройства позволяет уменьшить звон в линии передачи и шумы в системе за счет небольшой дополнительной задержки. Включение резистора нагрузки между выходом и шиной питания. Когда резистор нафузки включен, он предотвращает появление на выходном выводе плавающего напряжения при подаче на микросхему напряжения питания. Это полезно в том случае, когда выходные сигналы поступают на входы разрешения других логических устройств с низким активным уровнем, в отношении которых не предполагается, что в момент включения питания на них будет подан сигнал, имеющий активное значение. Образование программируемых пользователем выводов земли. Эта возможность фактически позволяет перераспределять I/0-выводы так, чтобы те или иные выводы были выводами земли, а вовсе не сигнальными выводами. Это оказывается полезным в быстродействующих устройствах с высокой скоростью изменения сигналов. Необходимость в дополнительных выводах земли возникает в тех случаях, когда имеют место большие броски тока, возникающие при одновременном переключении сигналов на нескольких выходах. Кроме этих особенностей, ИС семейства ХС9500 совместимы с внешними устройствами с напряжением питания 5 В и 3.3 В. Входной буфер и внутренняя логика работают от источника питания с напряжением V, равным 5 вольтам. В зависимости от напряжения питания внешних устройств, в выходном каскаде используется напряжение питания V, равное 5 В или 3.3 В. Обратите внимание, что включение резистора между выходом и шиной питания подтягивает напряжение на выходе до напряжения питания блока I/O, то есть до напряжения F(,q-Диоды D1 и D2 необходимы для фиксации выходного напряжения на уровне не выше значения V и не ниже уровня земли. За эти фанищл величина выходного напряжения могла бы выходить из-за звона в линии передачи. 10.5.4. Переключающая матрица Теоретически профаммируемая структура соединений внутри ИС типа CLD должна допускать соединение любого внутреннего выхода ПЛУ и любого внешнего входа с любым внутренним входом ПЛУ. Аналогично, должно быть возможным подключение любого выхода любого из внутренних ПЛУ к любому внешнему выводу. Но если присмотреться внимательнее, то становится ясно, что мы возвращаемся к той же самой проблеме , которая возникала бы при попытке создания ИС 128V64. Рис. 10.42 служит иллюстрацией требований, предъявляемых к переключающей матрице, на примере ИС ХС95108 - типичного представителя семейства ХС9500 фирмы Xilinx. У этой микросхемы имеются 108 выходов внутренних макроячеек и 108 внешних входных выводов, так что полное число сигналов, которые должны бьггь поданы на переключающую матрицу в качестве входных, составляет 216. Так как в ИС ХС95108 имеется 6 функциональных блоков с 36 входами каждый, то переключающая матрица должна иметь в случае наибольшей полноты 216 мультиплексоров с 216 входами каждый, так чтобы сигнал с выхода каждого мультиплексора поступал на один из входов матрицы И одного из функциональных блоков. Переключающая матрица, показанная на рисунке, может быть выполнена в микросхеме в виде прямоугольной структуры, у которой входы расположены по столбцам, а выходы - по строкам, с проходным транзистором (или логическим ключом) в каждой точке пересечения, позволяющим соединить данный вход с соответствующим выходом. Приведенный пример показывает, что это все же слишком большая структура: 216 строк и 216 столбцов! При современной технологии создания ИС с высокой плотностью размещения компонентов проблема состоит не столько в размерах кристалла, сколько в быстродействии устройства. Большое число транзисторов, включенных в каждой строке и в каждом столбце, обуславливает наличие значительной емкости, которая приводит к уменьшению быстродействия. Поэтому производители ИС типа CPLD ищут способы уменьшить размер переключающей матрицы. Глядя на рис. 10.42, можно увидеть, например, что не для каждого входа переключающей матрицы необходимо предусмотреть возможность его подключения к каждому выходу. Нужно лишь, чтобы каждый вход мог быть подключен к какому-либо входу каждого функционального блока, поскольку любой вход функционального блока может быть соединен с любым вентилем И матрицы И данного функционального блока. Но снова задача совсем не так проста, как мы только что ее сформулировали. Предположим, что сигнал на выходе переключающей матрицы для /-го входа рассматриваемого функционального блока (О < / < 35) вырабатывается простым 8-входовым мультиплексором, входы которого являются входами переключающей матрицы с номерами от 8/ до 8/ + 7. С помощью такой переключающей матрицы нельзя осуществить многие из вариантов межсхемных соединений. Например, подключение входов переключающей матрицы с номерами от О до 35 к тому же самому функционального блоку было бы невозможно. Как только вход О переключающей матрицы соединяется с входом О одного их функциональных блоков, входами переключающей матрицы с номерами от 1 до 7 уже нельзя воспользоваться. Таким образом, требования, предъявляемые к возможности осуществления с помощью переключающей матрицы тех или иных соединений, следует сформулировать более широко: для каждого функционального блока должно быть возможным подключение любой комбинации входов переключающей матрицы к какой-либо комбинации входов данного функционального блока. Переключающая матрица типичной ИС типа CPLD представляет собой компромисс между минимальной схемой мультиплексора и полной, неблокирующей структурой коммутационной матрицы. Если возможности переключающей мат- ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |