(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

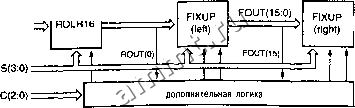

Читальный зал --> Программные средства foundation library IEEE: нее IEEE.std logic l164.all; entity rolrlS is port С СИ: In STD L0C.IC ?SCT0R(1S downto 0); S; in STD ..LOGIC.VECTOR (3 dovato 0); CIS: in 3TD..LCGIC; ОООТ: o t STD L0GIC.VECT0R(1S downto 0) end rolrl6: - Data inputs -- Sbift ajsount, 0-lS -- Shift direction, 0=>L, 1= Data bus output architecture roll6r arcb of rolrlfi is begin process(DIN, S, DIR) variable X, Y, Z: STD I,0GIC VECTOR(15 downto 0); variable CTRLO, CTiU.1, CTRL2, CTiU.3; .=TDJ,DGTC VECT0R(1 do-wnto 0); begi:i CTRLO := 3(0) & DIR; CTRil S(l) k DIR; CT.U2 := S(2) к DIP.; CTRLS :- S(3) к DIR; case CTRLO is when 00 I 01 X DIK; when 10 X := DIN (14 downto 0) к DIN (15); when 11 => X := DIN(O) к DIK{16 downto 1); when others => mill; end case; case CTRLI is when 00 I 01 => У X; when 10 => У c= X(13 dovinto 0) к X<1S downto 14); when 11 => Y := X(l downto 0) к X(i6 downto 2); when others => null; end case; case CTRL2 is when CO i 01 => Z := Y; when 10 => 7. := Y(ll downto 0) i Y(1S downto 12); when 11 => 7. := Y(3 downto 0) ft Y(15 downto 4); when others => null; end case; case CTRL3 is when 00 i 01 => DOm- <= Z; when 10 i 11 => DQin <= Z(7 downto 0) к 2(15 downto 8); when others >=> null; end case; end process; end roIlSr arch; DIN(15:0): ROUT(15:0)  z:>DOUT(15:0) Рис. 6.14. Блок-схема устройства быстрого сдвига там значение О или первоначальное значение бита, находившегося в крайнем правом разряде соответственно. Для логического или арифметического сдвига на п разрядов вправо мы должны присвоить левым и -1 битам значение О или первоначальное значение бита, находившегося в крайнем левом разряде соответственно. Табл. 6.19. Программа на языке VHDL для 16-разрядного устройства быстрого сдвига, выполняющего циклические сдвиги влево и вправо

.* , end fixup; architecture fixup.arch of fixup is begin process<DIN, S, FE8, FDAT) begin for i in 0 to 15 loop if (i < CONV.INTEGERCS)) and (FEN = 1) then DOUT(i) <= FDAT; else DOUT(i) <= DIK(i): end if; and loop; end process; end fixup.arch; Блок, соответствующий циклу for в табл. 6.20, синтезировать легко, но заранее нельзя быть уверенным, что его логика будет вполне подходящей. В частности, наличие операции < , выполняемой на каждом проходе цикла, может заставить синтезатор включить универсальный компаратор, сравнивающий значения величин, несмотря на то, что один из операндов является константой, и поэтому сигнал на каждом выходе можно бьшо бы получить с помощью небольшого числа вентилей. (Например, реализация логики 7 < CONV INTEGER {S) состоит всего лишь в подведении провода S {3)!) В рассуждении, вьшесенном за пределы основного текста и озаглавленном Последовательная структура схемы коррекции , говорится о структурном варианте этой функции. Как показано на рис. 6.14, наша стратегия состоит в том, чтобы вслед за устройством R0LR16, осуществляюшлм циклический сдвиг, включить схему коррекции FlXUP{left), которая заполняет нужные младшие разряды при логическом или арифметическом сдвиге влево, и схему коррекции FlXUP(right), которая заполняет нужные старшие разряды при логическом или арифметическом сдвиге вправо. В табл. 6.20 приведена поведенческая программа на языке VHDL для схемы коррекции при сдвиге влево. У нее имеются 16-разрядные входы и выходы дан-ньЕх DIN и DOUT соответственно. На входы управления поступают сигналы S, которыми задается величина сдвига, сигнал разрешения коррекции FEN и новая величина FDAT для вставления в корректируемые разряды выходных данных. Схема помещает значение корректирующего бита в каждый разряд данных на выходе DOUT (i), если i меньше S и коррекция разрешена; в противном случае на выходы схемы передаются значения битов на входе DIN (i) без изменений. Табл. 6.20. Поведенческая программа на языке VHDL для схемы коррекции при сдвиге влево library ХЕЕЕ; use IEEE.std.logic l164.all; use IEEE.std.logicarith.all; ПОСЛЕДОВАТЕЛЬНАЯ СТРУКТУРА СХЕМЫ КОРРЕКЦИИ Структурная архитектура схемы коррекции приведена в табл. 6.21. По существу, здесь определена итерационная схема, вырабатывающая 16-разрядный вектор FSEL с равным 1 значением FSEL (i), если i-й бит нуждается в коррекции. Процедура начинается с того, что биту FSEL (15) присваивается значение О, поскольку в этом разряде никогда не требуется коррекция. Для остальных значений i величина FSEL (i) должна равняться 1, если значение S равно i+1, и в том случае, когда биту FSEL (i+1) уже присвоено единичное значение. Таким образом, присваивание значений битам FSEL оператором generate создает последовательную цепочку 2-входовых вентилей ИЛИ: один из входов каждого вентиля ИЛИ предназначен для подачи 1, когда S=i (что обнаруживается по результату декодирования 4-входовым вентилем И), а другой вход каждого следующего вентиля ИЛИ соединен с выходом предыдущего вентиля ИЛИ. Оператор присваивания DOUT {i) создает 16 двухвходовых мультиплексоров, каждый из которых выбирает бит входных данных DIN (i) или корректирующий бит (FDAT) в зависимости от значения FSEL (i). Реализация схемы коррекции в виде последовательной цепочки оказывается компактной, но очень медленной по сравнению со схемой, в которой сигнал на каждом выходе FSEL вырабатывается двухуровневой логикой по выражениям вида сумма произведений . Однако в данном случае большая задержка не имеет значения, поскольку схема коррекции располагается в конце пути прохождения данных. Если все же быстродействие существенно, то можно воспользоваться бесплатным приемом, который позволяет уменьшить задержку вдвое (см. задачу 6.12). При сдвиге вправо коррекция начинается с противоположной стороны слова данных, поэтому может показаться, что необходима еще одна схема коррекции. Однако, как мы скоро увидим, для этого можно воспользоваться уже имеющейся схемой, если только изменить порядок следования входных и выходных битов на противоположный. Табл. 6.21. Структурная VHDL-архитектура схемы коррекции при сдвиге влево architecture fixup struc of fixup is signal FSEL: STD.LOGIC.VECTOR(15 dowHto 0); - Fixup select begin FSELCIS) <= 0; D0UT(15) <= DIS(15); Ul: for i in 14 dowHto 0 generate FSEL(i) <= -1 when CQNV.INTEGER(S) = i+1 else FSEL(i+l); DOUT(i) <= FDAT when (FSEL(i) = 1 and FEN = 1) else DIN(i); end generate; end fixup.struc; В табл. 6.22 приведена объединенная структурная архитектура полного 16-разрядного устройства быстрого сдвига с 6-ю режимами работы, в котором реализован подход, изображенный на рис. 6.14. Объявление объекта barrel 16 ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |