(926)274-88-54

Бесплатная доставка.

Бесплатная сборка.

График работы:

Ежедневно. С 8-00 до 20-00.

Почта: soft_hous@mail.ru

|

Звоните! (926)274-88-54 Бесплатная доставка. Бесплатная сборка. |

Ассортимент тканей График работы: Ежедневно. С 8-00 до 20-00. Почта: soft_hous@mail.ru |

|

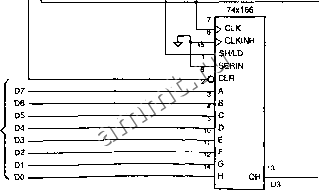

Читальный зал --> Программные средства foundation таймслота (timeslot), содержащих по 8 битов каждый. В каждом таймслоте передается в цифровом виде один речевой сигнал. Номера таймслотов и расположение битов внутри каждого из них отсчитываются от импульса сигнала SYNC. На рис. 8.56 представлена схема, осуществляющая преобразование параллельных данных в последовательный формат, указанный на рис. 8.55(a), с учетом деталей, приведенных на рис. (Ь). Две ИС 74x163 образуют счетчик по модулю 256, работающий в непрерывном режиме; этим счетчиком задается кадр. Пять старших разрядов счетчика указывают номер таймслота, а три младших разряда - номер бита в пределах таймслота. CLOCK RESET.L параллельные данные 74x163 >CLK CLR -гО LD ENP OA QB ОС QD RCO RC04 номер бита 74X163 74x10 > CLK -д-0 CLR -742 LD ENP ENT А В QA QB QC QD RCO Birr.L SYNC Ч номер таймслота SYNC  CLOCK SDATA / К при-*емнику Рис.8.56. Преобразование параллельного кода в последовательный с помощью регистра сдвига с параллельным вводом КАКОЙ БИТ ПЕРВЫЙ? В действительности, в большинстве последовательных каналов передачи оцифрованного речевого сигнала первым передается 7-й бит, поскольку он первым появляется на выходе аналого-цифрового преобразователя, переводящего речевой сигнал в цифровую форму. Однако, ради простоты, мы указываем в наших примерах, что первым передается 0-й бит, так что в состояние счетчика номер бита входит непосредственно. Регистр сдвига с параллельным вводом 74x166 осуществляет преобразование параллельного кода в последовательный. 0-й бит параллельных данных (D0-D7) подается на вход ИС 166, ближайший к выходу SDATA, так что биты передаются последовательно в порядке О, 7. При передаче 7-го бита в каждом таймслоте вырабатывается сигнал BIT7 L, который приводит к зафузке ИС 166 данными D0-D7. Значения сигналов на входах D0-D7 несущественны в течение всего времени, за исключением времени установления и времени удержания в окрестности того перепада в тактовом сигнале, на котором ИС 166 зафужается; интервалы времени, в пределах которых значения сигналов на входах данных безразличны, на временнь/х диафаммах заштрихованы. Из этого следует, что шиной, по которой поступают параллельные данные, в другое время можно пользоваться для решения каких-то других задач (см. задачу 8.54). В модуле-приемнике преобразование последовательных данных обратно в параллельный формат может осуществляться схемой, приведенной нарис. 8.57. Счетчик по модулю 256, состоящий из двух ИС 163, позволяет восстановить номера таймслотов и битов. Поскольку сигнал SINC вырабатывается в то время, когда счетчик в модуле-передатчике находится в состоянии 255, и по этому сигналу выполняется зафузка в счетчик модуля-приемника нулевого содержимого, оба счетчика переходят в нулевое состояние по одному и тому же фронту тактового сигнала. Старшие биты счетчика (номер таймслота) никак не используются на рисунке, но они могут позволить другим схемам в модуле-приемнике идентифицировать байты, удерживаемые на шине параллельных данных (PD0-PD7) в пределах того или иного таймслота. На рис. 8.58 приведены подробные временнь/е диафаммы для схемы, осуществляющей преобразование последовательного кода в параллельный. Полностью принятый байт присутствует на параллельном выходе регистра сдвига 74x164 в течение периода тактового сигнала, следующего за приемом последнего (7-го) бита в байте. В нашем примере параллельные данные дважды буферизованы {double-buffered data): будучи полностью приняты, они переносятся в регистр 74x377, на выходах которого PD0-PD7 они доступны другим частям системы в течение восьми полных периодов тактового сигнала до окончания приема следующего байта. Сигнал разрешения BITO L обеспечивает зафузку ИС 377 в надлежащий момент времени. При наличии дополнительных регистров и декодирования можно было бы загружать байты из различных таймслотов в соответствующие регистры, в которых каждый байт удерживался бы на протяжении 125 МКС (см. задачу 8.57). SYNC L ОТ передатчика CLOCK- SYNC- 4>i SDATA - 74x163 >CLK CLR 2C LD QC QD BC04 74x163 >CLK О CLR ENP ENT A В 74x164 >CLK fO CLR SERA SERB QA QB QC QD QE QF QG QH номер бита --U5 z BITO BtTO L НОМф таймслота >CLK 10 RD3 11 RD2 12 RD1 17 13 RDO ID 20 3D 4D 5D 6D 7D 8D IQ 2Q 30 4Q SO 6Q 7Q 8Q - PD7 - PD6 - PD6 - PD4 - PD3 - PD2 - PD1 PDO парал->лельные данные Рис. 8.57. Преобразование последовательного кода в параллельный с помощью регистра сдвига с параллельным выводом Представленные в параллельном формате принятые данные легко запоминать и модифицировать в других цифровых схемах; в разделе 10.1.6 будут приведены соответствующие примеры. В цифровой телефонии принятые параллельные данные преобразуются обратно в аналоговое напряжение, которое фильтруется и отправляется в телефонную трубку или на громкоговоритель в течение 125 мкс, то есть до тех пор, пока не поступит следующее выборочное значение речевого сигнала. ООО «Мягкий Дом» - это Отечественный производитель мебели. Наша профильная продукция - это диваны еврокнижка. Каждый диван можем изготовить в соответствии с Вашими пожеланияи (размер, ткань и материал). Осуществляем бесплатную доставку и сборку. Звоните! Ежедневно! (926)274-88-54 Продажа и изготовление мебели. Копирование контента сайта запрещено. Авторские права защищаются адвокатской коллегией г. Москвы. |